Home > On-Demand Archives > Theatre Talks >

Partitioning for Security

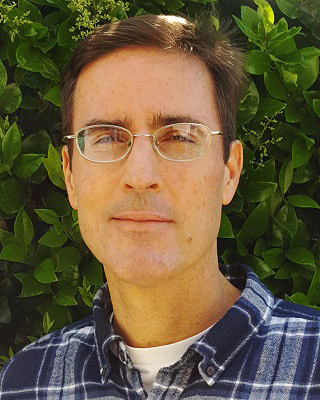

David Moore - Watch Now - EOC 2022 - Duration: 34:07

Thanks for watching. The chip manuals usually don't cover the MPU because it is defined by ARM in their docs. You can find them easily with Google and download the PDFs:

v7: "arm 0403e" and see section B3.5 Protected Memory System Architecture, PMSAv7

v8: "arm 100699"

Even better is to get Joseph Yiu's book The Definitive Guide to the ARM Cortex-M3 and Cortex-M4. It's the reference standard for the Cortex-M processors.

Thank you! Quick search and I found "ARM DDI 0403E.b" document with B3.5 section.

A mouse pointer would have helped to understand what you are talking about.

I agree, especially for the code snippets and tool output that would have been helpful. Thanks for your suggestion!

Thank you for your talk - I am programming ARM Cortex-M3 and Cortex-M4 and earlier I was skipping MPU part of the hardware in PDF chip documentation because it was relatively short.