Home > On-Demand Archives > Q&A Sessions >

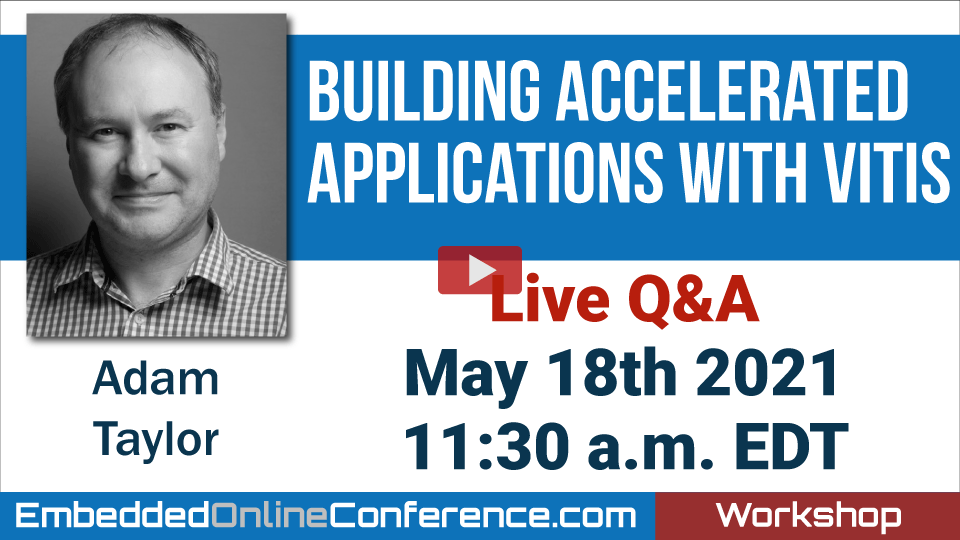

Live Q&A - Building Accelerated Applications with Vitis

Adam Taylor - Watch Now - EOC 2021 - Duration: 27:51

video stops at minutes 56:29, when launching hardware emulation. i have tried to reload the page several times but it always stops at the same point

EDIT: I can manually resume the video moving the time bar forward

You can find all the slides and lab material here

https://github.com/ATaylorCEngFIET/EOC_Vitis

This workshop is made available pre-recorded and will be followed by a Live Q&A

12:45:01 From EricS : Is OpenCL inherently limited to the host bandwidth? My target real-time application has an input data interface connected directly to the FPGA, and a output data interface also connected to the FPGA. I'd like to use C to program the FPGA. I'm ok using a host to configure the FPGA and check it's status and control a UI. But I don't want to have to transfer all of my data back and forth to the host! Especially as the host might not be sufficiently real-time. Is OpenCL and Vitis a good solution for this scenario, or should I stick with VHDL /Verilog with a few memory-mapped registers for talking to the host? 12:45:34 From Dave Nadler : Would this flow work for speech recognition or at least keyword recognition? 12:47:46 From Marian Szabo : What was the 300USD range board he mentioned while ago ? 12:49:58 From Michael Kirkhart : I believe this is the Ultra 96 board mentioned: https://www.avnet.com/shop/us/products/avnet-engineering-services/aes-ultra96-v2-g-3074457345638646173/ 12:50:17 From Michael Kirkhart : It shows a price of about $250 12:52:53 From Chris Venter : How would you implement DSP processing using Vitis - would you use OpenCL FFT libraries for instance or does the XRT library provide DSP primitives directly? 12:56:45 From Dave Nadler : Thanks Adam - Really educational! 12:58:10 From Radu Pralea : What would be the order of magnitude of a round trip latency for a setup you mentioned before (with FPGA in the middle, and the host at both ends) for a cheap platform you suggested ($300 board rather than a $3000 PCIe card)? 13:00:23 From Radu Pralea : got it, thanks. I wanted to use a x86 host :) 13:00:45 From Radu Pralea : yes, but expensive 13:01:21 From Radu Pralea : thank you 13:02:26 From Iván GB : Thank you

Does Xilinx support developing OpenCL applications with Vitis using FreeRTOS instead of Linux?